LMT043DNFFWD-NCA

LCD Module User Manual

Prepared by:

Checked by:

Approved by:

Yu

Date: 2019-06-20

Date:

Date:

Rev. Descriptions

Release Date

0.1

New release

2015-09-01

0.2

Update section 2,section 3 and section 10

2018-03-19

0.3

Update section 1

2018-10-18

0.4

Update section 8

RL:

www.topwaydisplay.com

Document Name: LMT043DNFFWD-NCA-Manual-Rev0.4

Page: 1 of 16

TOPWAY

LCD Module User Manual

LMT043DNFFWD-NCA

Table of Content

1. GENERAL SPECIFICATION .................................................................................................................... 3

2. BLOCK DIAGRAM .................................................................................................................................... 3

3. TERMINAL FUNCTIONS .......................................................................................................................... 4

4. ABSOLUTE MAXIMUM RATINGS ........................................................................................................... 4

5. ELECTRICAL CHARACTERISTICS ........................................................................................................ 5

5.1

DC C HARACTERISTICS ......................................................................................................................... 5

5.2

T OUCH PANEL C HARACTERISTICS ......................................................................................................... 5

6. AC CHARACTERISTICS .......................................................................................................................... 5

6.1

8080 M ODE T IMING ............................................................................................................................. 5

6.2

SPI M ODE T IMING ................................................................................................................................ 6

6.3

R ESET T IMING ..................................................................................................................................... 8

7. TOUCH PANEL CONTROLLER TIMING CHARACTERISTICS ............................................................. 8

7.1

ADS7843 D IGITAL T IMING .................................................................................................................... 8

7.2

T IMING DIAGRAM .................................................................................................................................. 9

8. OPTICAL CHARACTERISTICS................................................................................................................ 9

9. FUNCTION SPECIFICATIONS ............................................................................................................... 11

9.1

C OMMAND S UMMARY ......................................................................................................................... 11

10.

TOUCH PANEL DESIGN PRECAUTIONS ......................................................................................... 14

11.

PRECAUTIONS OF USING LCD MODULES ..................................................................................... 15

APPENDIX A INSPECTION ITEMS AND CRITERIA FOR APPEARANCE DEFECTS ................................ 15

RL:

www.topwaydisplay.com

Document Name: LMT043DNFFWD-NCA-Manual-Rev0.4

Page: 2 of 16

TOPWAY

LCD Module User Manual

LMT043DNFFWD-NCA

1. General Specification

Screen Size(Diagonal) :

4.3 inch

Resolution :

480(RGB) x 272

Interface :

8bit MCU Interface

Color Depth :

16.7M color (24bit)

Dot Pitch :

0.198 x 0.198 (mm)

Pixel Configuration :

RGB Stripe

Display Mode :

Transmissive / Positive

Surface Treatment :

Anti-Glare Treatment

Viewing Direction :

12 o’clock ( gray scale inverse )

Outline Dimension :

121.0x70.0x12.2 (mm)

Active Area :

95.4 x 53.86 (mm)

Backlight :

LED, White

Operating Temperature :

-20 ~ +70°C

Storage Temperature :

-30 ~ +80°C

Note: Backlight color may slightly change over temperature and driving voltage.

2. Block Diagram

DIN, DOUT, DCLK

TP controller

Touch Panel

/PENIRQ, BUSY, /CSTP

AD7843

Backlight

Backlight

BL_ADJ

Driver

/RD, /WR, /CS, A0

D0~D7

480(x3) x 272 pixels

TFT Panel

/RES, TE

SPI_EN

VDD, VSS

Power Circuit

Source Driver

RL:

www.topwaydisplay.com

Document Name: LMT043DNFFWD-NCA-Manual-Rev0.4

Page: 3 of 16

TOPWAY

LCD Module User Manual

LMT043DNFFWD-NCA

3. Terminal Functions

Terminal (K1)

Pin

Pin

8bit MCU Mode (Default)

SPI Mode

No.

Name

I/O

Description

Description

1

VSS

Power Input

Power Supply GND (0V)

2

3

VDD

Power Input

Positive Power Supply(3.3V)

4

Access Mode

5

A0

Input

A0=High: Accessing Data

Keep open

A0=Low: Accessing Address

6

/CS

Input

Chip Select

/CS=Low: Data IO is enabled

Reset

7

/RES

Input

/RES=Low: Reset

/RES=High: Normal operation

8

D0(SI)

Serial input

9

D1(SO)

Serial output

:

:

Bi-directional I/O

8-bit Bi-directional data bus

Keep open

14

D6

Keep open

15

D7

Keep open

16

TE

Output

TE Signal

17

/RD

Input

Read Enable, active Low

Keep open

18

/WR(SCK)

Input

Write Enable, active Low

Serial clock

19

BL_ADJ

Input

Backlight Driver enable signal, active High, PWM(*2)can be

possible

20

SPI_EN

Input

Keep open

SPI Enable, active high

21

/PENIRQ

Output

Pen Interrupt (*3)(*4)

22

DOUT

Output

Data Output(*4)

23

BUSY

Output

Busy Output(*4)

24

DIN

Input

Data Input(*4)

25

/CSTP

Input

Chip Select, also for initiating the conversions(*4)

26

DCLK

Input

Clock Input for Serial Data & conversions(*4)

Note.

*1. Tear signal may leave open when not use

*2. The PWM frequency is between 200Hz and 500Hz.

*3. Pulled-up by internal resistor

*4. It is Touch Panel Controller’s communication interface

4. Absolute Maximum Ratings

Items

Symbol

Min.

Max.

Unit

Condition

Supply Voltage

V DD

-0.2

3.7

V

V SS = 0V

Input Voltage

V IN

-0.2

3.7

V

V SS = 0V

Operating Temperature

T OP

-20

+70

℃

No Condensation

Storage Temperature

T ST

-30

+80

℃

No Condensation

Caution:

Any Stresses exceeding the Absolute Maximum Ratings may cause substantial damage to the device. Functional

operation of this device at other conditions beyond those listed in the specification is not implied and prolonged exposure

to extreme conditions may affect device reliability.

RL:

www.topwaydisplay.com

Document Name: LMT043DNFFWD-NCA-Manual-Rev0.4

Page: 4 of 16

TOPWAY

LCD Module User Manual

LMT043DNFFWD-NCA

5. Electrical Characteristics

5.1 DC Characteristics

V SS =0V, V DD =3.3V, T OP =25 ℃

Items

Symbol

MIN.

TYP.

MAX.

Unit

Applicable Pin

Operating Voltage

V DD

2.8

3.3

3.6

V

VDD

Input High Voltage

V IH

-

-

VDD

V

Input pins, Bi-direction pins

Input Low Voltage

V IL

VSS

-

-

V

Input pins, Bi-direction pins

Output High Voltage

V OH

2.6

-

-

V

Bi-direction pins (*1)

Output Low Voltage

V OL

-

-

0.6

V

Bi-direction pins (*2)

Operating Current

I DD

-

230

500

mA

On Backlight Power on status

Note:

*1. Never Apply logic signal before the VDD supply.

*2. VDD setting should match the signals voltage

5.2 Touch panel Characteristics

Items

MIN.

TYP.

MAX.

Unit

Note

Surface hardness

3

-

-

H

-

Operating Force

30

-

160

g

-

Life Time

-

1,000,000

-

times

-

linearity

-1.5

-

+1.5

%

-

Transparency

78

-

-

%

-

Operation temperature

-20

-

70

℃

-

Storage temperature

-30

-

80

℃

-

6. AC Characteristics

6.1 8080 Mode Timing

A0

/CS Control

/CS

/WR

/RD

/RD,WR/ Control

/CS

/WR

/RD

Figure 2

RL:

www.topwaydisplay.com

Document Name: LMT043DNFFWD-NCA-Manual-Rev0.4

Page: 5 of 16

TOPWAY

LCD Module User Manual

LMT043DNFFWD-NCA

3.3 Volt

Symbol

Parameter

Units

Min

Max

t1

A0 setup time to /CS (/WR, /RD)

1

-

ns

t2

/WR, /RD (/CS) setup time to /CS (/WR, /RD)

1

-

ns

t3

DB[7:0] setup time to /CS (/WR) rising edge: write cycle

1

-

ns

t4

DB[7:0] hold time from /CS (/WR) rising edge: write cycle

7

-

ns

t5w

/WR (/CS) hold time from /CS (/WR) rising edge: write cycle

3

-

ns

t5r

/RD (/CS) hold time from /CS (/RD) rising edge: read cycle

0

-

ns

t6

A0 hold time from /CS (/WR, /RD) rising edge

4

-

ns

t7

/CS (/RD) falling edge to DB[7:0] driven: read cycle

-

15

ns

t8

/CS (/RD) falling edge to valid Data: read cycle

-

4xT mclk +17

ns

t9

DB[7:0] hold time from /CS (/RD) rising edge: read cycle

2

12

ns

t10w

End of write to next read/write

5

-

ns

t10r

End of read to next read/write

T mclk +9

-

ns

t11w

/CS (/WR) pulse width for write cycle

3

-

ns

t12w

/CS (/WR) rise to next /CS (/WR) rise: write cycle

3xT mclk +6

-

ns

Note: T mclk = period of internal MCLK clock signal.

Indirect 8-bit Function Select:

A0

/WR

/RD

Comments

0

0

1

Command Write (register address)

1

0

1

Data (Parameter) Write

0

1

0

inhibit

1

1

1

Data (Parameter) Read

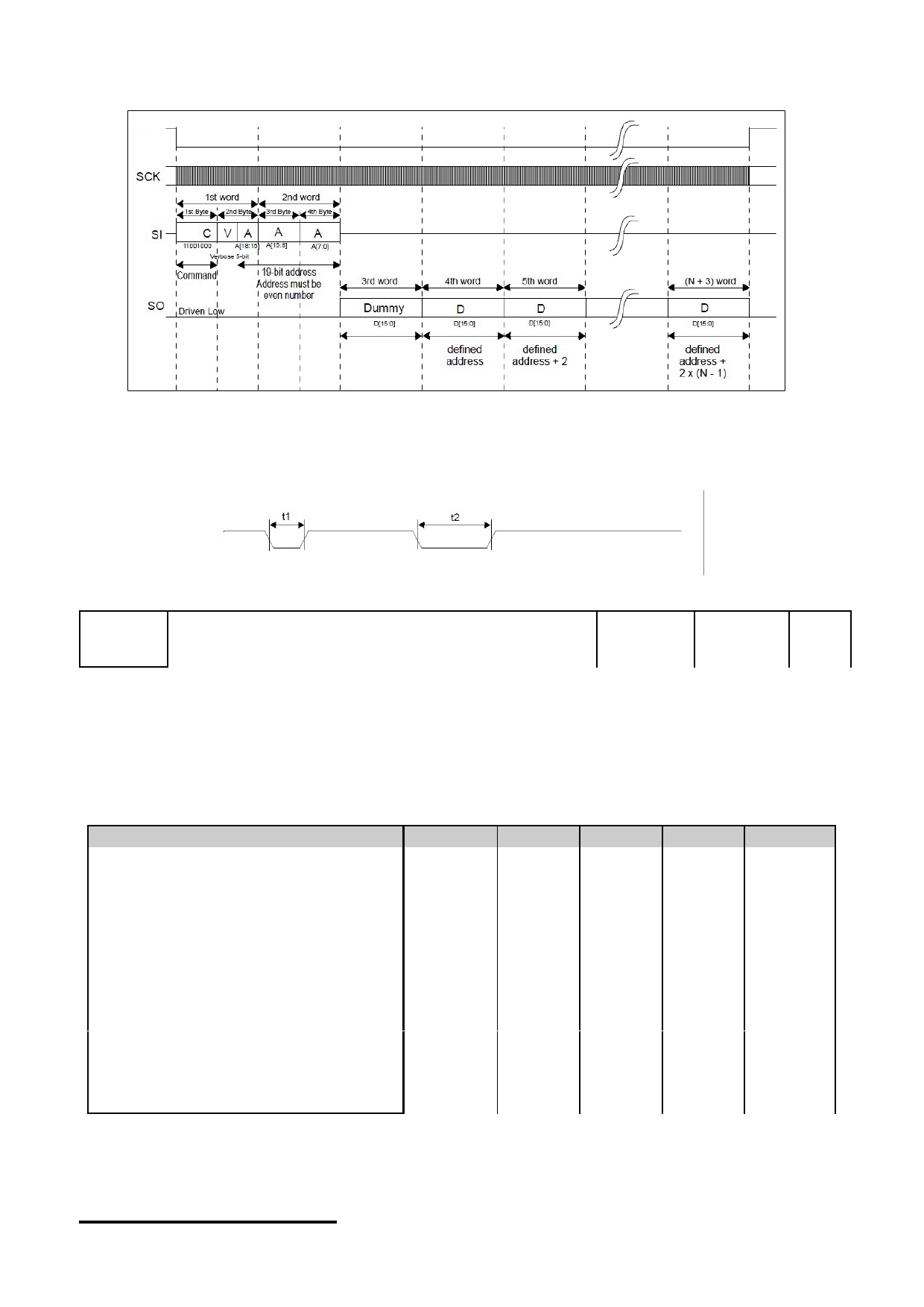

6.2 SPI Mode Timing

/CS

Figure 3

3.3 Volt

Symbol

Parameter

Units

Min

Max

t1

Chip select setup time

2

-

ns

t2

SI Data setup time

1

-

ns

t3

SI Data hold time

7

-

ns

t4

Serial clock pulse width low (high)

15

-

ns

t5

Serial clock pulse width high (low)

15

-

ns

t6

Serial clock period

30

-

ns

t7

Chip select hold time

7

-

ns

t8

Chip select de-assert to reassert

2

-

ns

t9

SCK falling edge to SO hold time

3

10

ns

RL:

www.topwaydisplay.com

Document Name: LMT043DNFFWD-NCA-Manual-Rev0.4

Page: 6 of 16

TOPWAY

LCD Module User Manual

LMT043DNFFWD-NCA

SPI Function Select:

Command

Comments

10000000

8-bit Write

11000000

8-bit Read

10001000

16-bit Write

11001000

16-bit Read

the other

reserved

Write Procedure:

SPI 8bit Write Sequence:

/CS

Figure 4

SPI 16bit Write Sequence:

/CS

Figure 5

Read Procedure:

SPI 8bit Read Sequence:

/CS

Figure 6

RL:

www.topwaydisplay.com

Document Name: LMT043DNFFWD-NCA-Manual-Rev0.4

Page: 7 of 16

TOPWAY

LCD Module User Manual

LMT043DNFFWD-NCA

SPI 16bit Read Sequence:

/CS

Figure 7

6.3 Reset Timing

/RES

Figure 8

Symbol

Parameter

Min

Max

Units

t1

Reset Pulse Width is ignored

-

42

ns

t2

Active Reset Pulse Width (see Note)

150

-

ns

Note: The Reset input should be held low for longer than 150ns to guarantee reset.

For more information and details please refer to LCD controller (S1D13L01) datasheet.

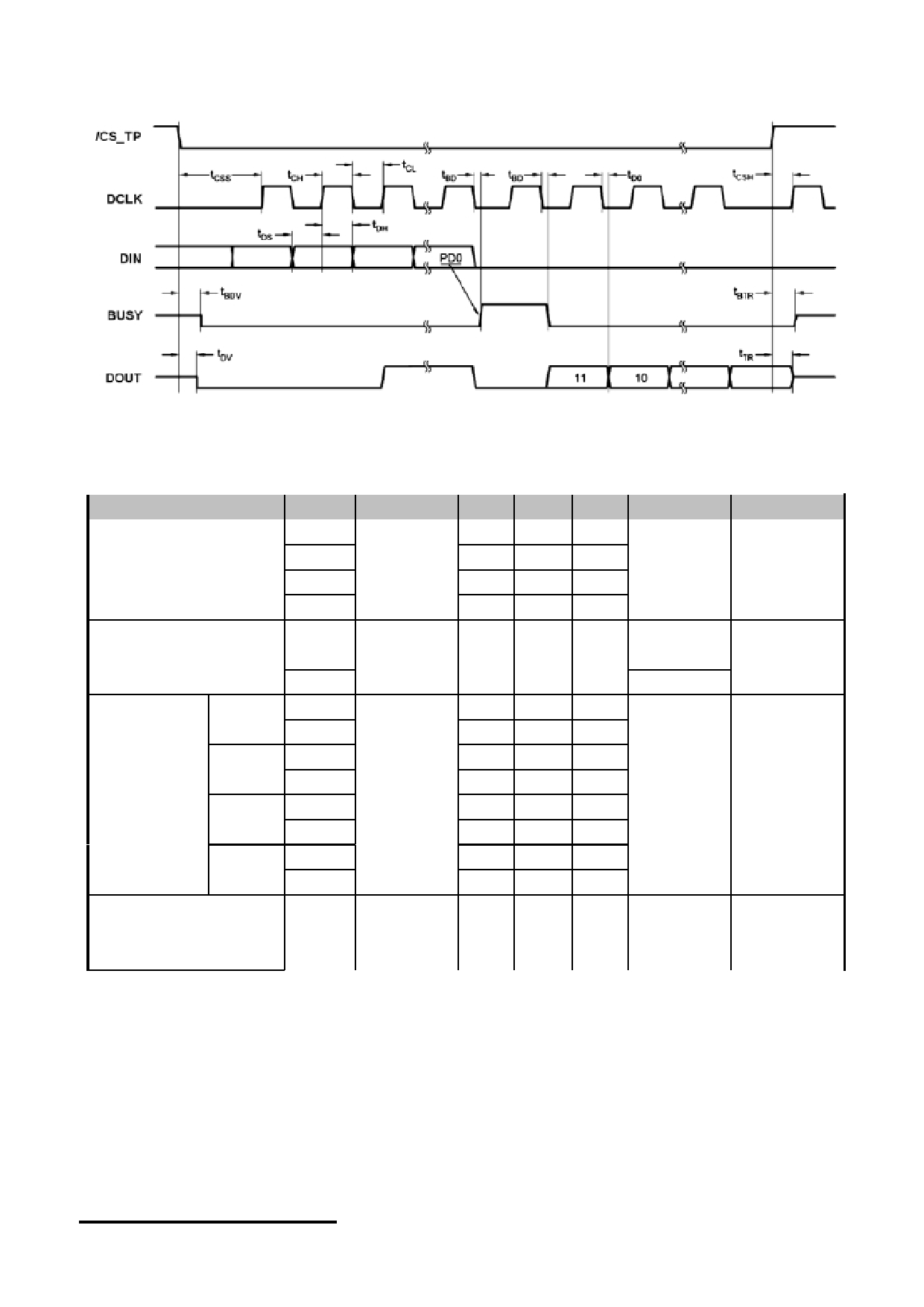

7. Touch Panel Controller Timing Characteristics

7.1 ADS7843 Digital Timing

Item

Symbol

MIN.

TYP.

MAX.

Unit

Acquisition Time

t ACQ

1.9

-

-

us

DIN Valid Prior to DCLK Rising

t DS

125

-

-

ns

DIN Hold After DCLK HIGH

t DH

13

-

-

ns

DCLK Falling to DOUT Valid

t DO

-

-

250

ns

/CS_TP Falling to DOUT Enabled

t DV

-

-

160

ns

/CS_TP Rising to DOUT Disabled

t TR

-

-

250

ns

/CS_TP Falling to First DCLK Rising

t CSS

125

-

-

ns

/CS_TP Rising to DCLK Ignored

t CSH

10

-

-

ns

DCLK HIGH

t CH

250

-

-

ns

DCLK LOW

t CL

250

-

-

ns

DCLK Falling to BUSY Rising

t BD

-

-

250

ns

/CS_TP Falling to BUSY Enabled

t BDV

-

-

160

ns

/CS_TP Rising to BUSY Disabled

t BTR

-

-

250

ns

Note. Please Refer to ADS7843E datasheet for details.

RL:

www.topwaydisplay.com

Document Name: LMT043DNFFWD-NCA-Manual-Rev0.4

Page: 8 of 16

TOPWAY

LCD Module User Manual

LMT043DNFFWD-NCA

7.2 Timing diagram

8. Optical Characteristics

Item

Symbol

Condition

MIN.

TYP.

MAX.

UNIT

Note.

θ T

60

70

-

Viewing angle

θ B

40

50

-

(CR ≥ 10)

degree

Note 2

θ L

60

70

-

θ R

60

70

-

Contrast ratio

CR

θ=0 o

400

500

-

-

Note 1,3

T on

msec

Response Time

25 ℃

-

20

30

Note 1,4

T off

msec

X

0.265 0.315 0.365

White

Y

0.285 0.335 0.385

X

0.531 0.581 0.631

Red

Y

Backlight

0.295 0.345 0.395

Chromaticlty

is on

Note 1,5

X

0.298 0.348 0.395

Green

Y

0.531 0.581 0.631

X

0.103 0.153 0.203

Blue

Y

0.045 0.095 0.145

NTSC

-

50

%

Note 5

Luminance uniformity

U

-

75

-

%

Note 1,7

Luminance

L

300

-

cd/m 2

Note :

The parameter is slightly changed by temperature, driving voltage and materiel

Please see the Notes for testing conditions

RL:

www.topwaydisplay.com

Document Name: LMT043DNFFWD-NCA-Manual-Rev0.4

Page: 9 of 16

TOPWAY

LCD Module User Manual

LMT043DNFFWD-NCA

Note 1:

The data are measured after LEDs are turned on for 5

minutes. LCM displays full white. The brightness is the

average value of 9 measured spots. Measurement

equipment PR-705 (Φ8mm)

Measuring condition:

- Measuring surroundings: Dark room

- Measuring temperature: Ta=25 ℃ .

- Adjust operating voltage to get optimum

contrast at the center of the display.

Measured value at the center point of LCD panel after more

than 5 minutes while backlight turning on.

Note 2: reference Figure5

The luminance uniformity is calculated by using following

formula.

△ Bp = Bp (Min.) / Bp (Max.)×100 (%)

Bp (Max.) = Maximum brightness in 9 measured

Figure 9

spots

Bp (Min.) = Minimum brightness in 9 measured spots .

Note 3: reference Figure6

The definition of viewing angle:

Refer to the graph below marked by θ and Ф

Note 4:

The definition of contrast ratio (Test LCM using PR-705):

Figure 10

Contrast Luminance When LCD is at “White” state

Ratio(CR)= Luminance When LCD is at “Black” state

(Contrast Ratio is measured in optimum common electrode

voltage)

Note 5: reference Figure7

Definition of Response time. (Test LCD using DMS501):

The output signals of photo detector are measured

when the input signals are changed from

Figure 11

“black” to “white”(falling time)

and from “white” to “black”(rising time), respectively.

The response time is defined as

the time interval between the 10% and 90% of

amplitudes.Refer to figure as below.

Note 6: reference Figure8

Definition of Color of CIE Coordinate and NTSC Ratio.

Color gamut:

Area of RGB triangle

S=

X100%

Area of NTSC triangle

Figure 12

RL:

www.topwaydisplay.com

Document Name: LMT043DNFFWD-NCA-Manual-Rev0.4

Page: 10 of 16

TOPWAY

LCD Module User Manual

LMT043DNFFWD-NCA

9. Function Specifications

9.1 Command Summary

Command

Para-

meter

HEX

Descriptions

Power Save

P1 60804 0 0 0

A[7:0]-> A[15:8] -> A[18:16]

Power Save Configuration Register

D[7:0]

1 0 0 n/a n/a n/a n/a n/a n/a Power Save Bit[1:0] = 00 , PSM0 mode

P2 D[15:8]

Bit[1:0] = 01 , PSM1 mode

1 0 0 n/a n/a n/a n/a n/a n/a n/a n/a

Bit[1:0] = 1x , NMM mode

Software

P1 60806 0 0 0

A[7:0]-> A[15:8] -> A[18:16]

Software Reset Register(Write Only)

Reset

D[7:0]

1 0 0 n/a n/a n/a n/a n/a n/a n/a n/a

D[15:8]

Softw Bit[8] = 0 , no effect in hardware

P2

1 0 0 n/a n/a n/a n/a n/a n/a n/a are Bit[8] = 1 , all registers are reset to default values

Reset

PLL Setting 0 P1 60810 0 0 0

A[7:0]-> A[15:8] -> A[18:16]

PLL Setting Register 0

D[7:0]

PLL PLL Bit[0] = 0 , the PLL is disabled

1 0 0 n/a n/a n/a n/a n/a n/a Bypa Enabl Bit[0] = 1 , the PLL enabled

Bit[1] = 0 , PLL is selected

P2

ss

e

D[15:8]

PLL

Bit[1] = 1 , CLKI is selected

1 0 0 Lock n/a n/a n/a n/a n/a n/a n/a Bit[15] = 0 , the PLL output is not stable

(RO)

Bit[15] = 1 , the PLL output is stable

PLL Setting 1 P1 60812 0 0 0

A[7:0]-> A[15:8] -> A[18:16]

PLL Setting Register 1

D[7:0]

1 0 0

M-Divider

Bit[9:0] 000h,001h … … 019h,020h : 1:1 ,2:1 … … 33:1(M-Divide Ratio).

P2 D[15:8]

021h to 13Fh: Reserved, PFDCLK = CLKI ÷ (M-Divider + 1)

1 0 0 n/a n/a

N-Counter

M-Divider

Bit[13:10] , must be set to 0000

PLL Setting 2 P1 60814 0 0 0

A[7:0]-> A[15:8] -> A[18:16]

PLL Setting Register 2

D[7:0]

1 0 0

L-Counter

Bit[9:0] , must be set between 010h ~ 041h. , and get the M-Divide Ratio

P2

D[15:8]

1 0 0 n/a n/a n/a n/a n/a n/a L-Counter from 17:1 to 66:1. POCLK = (L-Counter + 1) x (N-Counter + 1) x PFDCLK

Internal Clock P1 60816 0 0 0

A[7:0]-> A[15:8] -> A[18:16]

Internal Clock Configuration Register

Configuration

D[7:0]

P2

1 0 0 n/a n/a n/a n/a n/a PCLK Divide Select Bit[3:0] = 0000b,0001b … … 1110b,1111b : 1:1 ,2:1 … … 16:1(MCLK to

D[15:8]

1 0 0 n/a n/a n/a n/a n/a n/a n/a n/a PCLK Frequency Ratio)

Panel Setting P1 60820 0 0 0

A[7:0]-> A[15:8] -> A[18:16]

Panel Setting Miscellaneous Register

Miscellaneous

D[7:0]

Panel

Panel Bit[0] = 0 , TFT panel is disable

PCLK

Data Panel Data Port Bit[0] = 1 , TFT panel is enable

1 0 0 DE Polarity Polari n/a

Enabl

Width

Enabl Bit[2:1] = 01 , TFT 16-bit

ty

e

e

Bit[2:1] = 10 , TFT 18-bit

D[15:8]

Bit[2:1] = 11 , TFT 24-bit

Bit[3] = 0 , panel data is disable

P2

Bit[3] = 1 , panel data is enable

Bit[5] = 0, the LCD data outputs transition on the rising edge of PCLK

1 0 0 n/a n/a n/a n/a n/a n/a n/a n/a Bit[5] = 1 , the LCD data outputs transition on the falling edge of PCLK

Bit[7:6] = 00 , DE Polarity Low active

Bit[7:6] = 01 , DE Polarity High active

Bit[7:6] = 10 , DE Polarity Fixed to Low

Bit[7:6] = 11 , DE Polarity Fixed to High

Display

P1 60822 0 0 0

A[7:0]-> A[15:8] -> A[18:16]

Display Settings Register

Settings

D[7:0]

Displ

Panel Bit[0] = 0 , HS, VS, DE and PCLK are fixed to H or L and the display pipes

TE

Displ

ay

SW Interf are disabled

Statu

1 0 0

TE Function ay

n/a Blank Video ace Bit[0] = 1 , enable the panel output and display pipes

s

Blank

Polari Invert Enabl Bit[1] = 0 , video data is normal

(RO)

ty

es Bit[1] = 1 , video data is inverted

D[15:8]

Bit[2] = 0 , the display blank function operates normally

Bit[2] = 1 , the display blank function switches polarity

Bit[4] = 0 , the LCD data is masked

Bit[4] = 1 , all applicable LCD data outputs are forced to zero or one

P2

Bit[6:5] = 00b , TE output is disabled and the pin output is low

TE

Bit[6:5] = 01b , TE output is high (1) when the display is in the Vertical

Outp

Non-Display Period (VNDP) and low (0) when the display is in Vertical

1 0 0 n/a n/a n/a n/a n/a n/a n/a ut Pin

Display Period (VDISP)

Disab

Bit[6:5] = 10b , Line Count

le

Bit[6:5] = 11b , Reserved

Bit[7] = 0 , the selected condition in not occurring

Bit[7] = 1 , the selected condition in not occurring

Bit[8] = 0 , TE is output

Bit[8] = 1 , TE is not output

HDISP

P1 60824 0 0 0

A[7:0]-> A[15:8] -> A[18:16]

Horizontal Display Width Register (HDISP)

D[7:0]

Horizontal Display Width

P2

1 0 0 n/a

Bit[6:0] = horizontal display width in pixels ÷ 8

D[15:8]

1 0 0 n/a n/a n/a n/a n/a n/a n/a n/a

HNDP

P1 60826 0 0 0

A[7:0]-> A[15:8] -> A[18:16]

Horizontal Non-Display Period Register (HNDP)

D[7:0]

1 0 0 n/a

Horizontal Non-Display Period

P2

Bit[6:0] = horizontal non-display period in PCLK’s

D[15:8]

1 0 0 n/a n/a n/a n/a n/a n/a n/a n/a

VDISP

P1 60828 0 0 0

A[7:0]-> A[15:8] -> A[18:16]

Vertical Display Height Register (VDISP)

D[7:0]

1 0 0

Vertical Display Height

P2

D[15:8]

Vertical

Bit[9:0] = vertical display height in lines

1 0 0 n/a n/a n/a n/a n/a n/a

Display

Height

VNDP

P1 6082A 0 0 0

A[7:0]-> A[15:8] -> A[18:16]

Vertical Non-Display Period Register (VNDP)

D[7:0]

1 0 0

Vertical Non-Display Period

P2

Bit[7:0] = vertical non-display period in lines

D[15:8]

1 0 0 n/a n/a n/a n/a n/a n/a n/a n/a

RL:

www.topwaydisplay.com

Document Name: LMT043DNFFWD-NCA-Manual-Rev0.4

Page: 11 of 16

TOPWAY

LCD Module User Manual

LMT043DNFFWD-NCA

Command

Para-

meter

HEX

Descriptions

HSW

P1 6082C 0 0 0

A[7:0]-> A[15:8] -> A[18:16]

HS Pulse Width Register (HSW)

D[7:0]

HS

Pulse

1 0 0

HS Pulse Width

Bit[6:0] = HS pulse width in PCLK’s

P2

Polari

Bit[7] = 0 , the horizontal sync signal is active low

ty

Bit[7] = 1 , the horizontal sync signal is active high

D[15:8]

1 0 0 n/a n/a n/a n/a n/a n/a n/a n/a

HPS

P1 6082E 0 0 0

A[7:0]-> A[15:8] -> A[18:16]

HS Pulse Start Position Register (HPS)

D[7:0]

HS Pulse Start Position

P2

1 0 0 n/a

Bit[6:0] = HS pulse start position in PCLK’s

D[15:8]

1 0 0 n/a n/a n/a n/a n/a n/a n/a n/a

VSW

P1 60830 0 0 0

A[7:0]-> A[15:8] -> A[18:16]

VS Pulse Width Register (VSW)

D[7:0]

VS

Pulse

1 0 0

n/a

VS Pulse Width

Bit[5:0] = VS pulse width in lines

P2

Polari

Bit[7] = 0 , the vertical sync signal is active low

ty

Bit[7] = 1 , the vertical sync signal is active high

D[15:8]

1 0 0 n/a n/a n/a n/a n/a n/a n/a n/a

VPS

P1 60832 0 0 0

A[7:0]-> A[15:8] -> A[18:16]

VS Pulse Start Position Register (VPS)

D[7:0]

VS Pulse Start Position

P2

1 0 0

Bit[7:0] = VS pulse start position in lines

D[15:8]

1 0 0 n/a n/a n/a n/a n/a n/a n/a n/a

TE Line Count P1 60834 0 0 0

A[7:0]-> A[15:8] -> A[18:16]

TE Line Count Register

D[7:0]

1 0 0

TE Line Count

These bits specify the line count value that is compared with the internal

P2 D[15:8]

TE Line

1 0 0 n/a n/a n/a n/a n/a n/a

vertical line counter

Count

Main Layer

P1 60840 0 0 0

A[7:0]-> A[15:8] -> A[18:16]

Main Layer Setting Register

Setting

D[7:0]

Main Layer

Main Layer Color

1 0 0 n/a n/a n/a

Rotation

Depth

Bit[2:0] = 000b, RGB 8:8:8 (default)

Select

Bit[2:0] = 001b, RGB 5:6:5

D[15:8]

Multi-

Bit[2:0] = 010b/011b/111b, Reserved

Byte

Bit[2:0] = 100b, 24 bpp + LUT1

Layer

Bit[2:0] = 101b, 16 bpp + LUT1

Regis

Bit[2:0] = 110b, 8 bpp + LUT1

P2

ters

Bit[4:3] = 00b, 0° (Normal)

Sync

1 0 0 n/a n/a n/a n/a n/a n/a n/a

Bit[4:3] = 01b, 90°

hrono

Bit[4:3] = 10b, 180°

us

Bit[4:3] = 11b, 270°

Latch

Bit[8] = 0, Synchronous latching of multi-byte layer registers is enabled

ing

Bit[8] = 1, Synchronous latching of multi-byte layer registers is disabled

Disab

le

Main Layer

P1 60842 0 0 0

A[7:0]-> A[15:8] -> A[18:16]

Main Layer Start Address Register 0

Start Address

D[7:0]

1 0 0

Main Layer Start Address

Bit[15:0] is Bit[15:0] of Main Layer Start Address ,but Bit[1:0] must be set

0

P2

D[15:8]

1 0 0

Main Layer Start Address

to 00b

Main Layer

P1 60844 0 0 0

A[7:0]-> A[15:8] -> A[18:16]

Main Layer Start Address Register 1

Start Address

D[7:0]

Main Layer Start

1 0 0 n/a

n/a

n/a

n/a

1

P2

Address

Bit[2:0] is Bit[18:16] of Main Layer Start Address

D[15:8]

1 0 0 n/a n/a n/a n/a n/a n/a n/a n/a

Main Layer

P1 60846 0 0 0

A[7:0]-> A[15:8] -> A[18:16]

Main Layer Width Register

Width

D[7:0]

1 0 0

Main Layer Width

P2 D[15:8]

Main Layer Read Only

1 0 0 n/a n/a n/a n/a n/a n/a

Width

Main Layer

P1 60848 0 0 0

A[7:0]-> A[15:8] -> A[18:16]

Main Layer Height Register

Height

D[7:0]

1 0 0

Main Layer Height

P2 D[15:8]

Main Layer Read Only

1 0 0 n/a n/a n/a n/a n/a n/a

Height

PIP Layer

P1 60850 0 0 0

A[7:0]-> A[15:8] -> A[18:16]

PIP Layer Setting Register

Setting

D[7:0]

1 0 0 n/a n/a n/a n/a n/a n/a n/a n/a Bit[2:0] = 000b, RGB 8:8:8 (default)

D[15:8]

Bit[2:0] = 001b, RGB 5:6:5

Bit[2:0] = 010b/011b/111b, Reserved

Bit[2:0] = 100b, 24 bpp + LUT1

PIP Layer

Bit[2:0] = 101b, 16 bpp + LUT1

P2

PIP Layer Color

1 0 0 n/a n/a n/a

Rotation

Bit[2:0] = 110b, 8 bpp + LUT1

Depth

Select

Bit[4:3] = 00b, 0° (Normal)

Bit[4:3] = 01b, 90°

Bit[4:3] = 10b, 180°

Bit[4:3] = 11b, 270°

PIP Layer

P1 60852 0 0 0

A[7:0]-> A[15:8] -> A[18:16]

PIP Layer Start Address Register 0

Start Address

D[7:0]

1 0 0

PIP Layer Start Address

Bit[15:0] is Bit[15:0] of Main Layer Start Address ,but Bit[1:0] must be set

0

P2

D[15:8]

1 0 0

PIP Layer Start Address

to 00b

PIP Layer

P1 60854 0 0 0

A[7:0]-> A[15:8] -> A[18:16]

PIP Layer Start Address Register 1

Start Address

D[7:0]

1 0 0 n/a n/a n/a n/a n/a n/a n/a n/a

1

P2 D[15:8]

PIP Layer Start

Bit[2:0] is Bit[18:16] of Main Layer Start Address

1 0 0 n/a n/a n/a n/a n/a

Address

PIP Layer

P1 60856 0 0 0

A[7:0]-> A[15:8] -> A[18:16]

PIP Layer Width Register

Width

D[7:0]

1 0 0

PIP Layer Width

Bit[9:] = PIP Layer Horizontal Display Period in number of pixels PIP

P2 D[15:8]

PIP Layer

1 0 0 n/a n/a n/a n/a n/a n/a

Layer Horizontal Display Period in number of pixels

Width

RL:

www.topwaydisplay.com

Document Name: LMT043DNFFWD-NCA-Manual-Rev0.4

Page: 12 of 16

TOPWAY

LCD Module User Manual

LMT043DNFFWD-NCA

Command

Para-

meter

HEX

Descriptions

PIP Layer

P1 60858 0 0 0

A[7:0]-> A[15:8] -> A[18:16]

PIP Layer Height Register

Height

D[7:0]

1 0 0

PIP Layer Height

P2 D[15:8]

PIP Layer Bit[9:] = PIP Layer Vertical Display Period in number of lines

1 0 0 n/a n/a n/a n/a n/a n/a

Height

PIP Layer X

P1 6085A 0 0 0

A[7:0]-> A[15:8] -> A[18:16]

PIP Layer X Start Position Register

Start Position

D[7:0]

1 0 0

PIP Layer X Start Position

P2

D[15:8]

PIP Layer X

These bits specify X start position of the PIP Layer on the panel, in lines

1 0 0 n/a n/a n/a n/a n/a n/a

Start

Position

PIP Layer Y

P1 6085C 0 0 0

A[7:0]-> A[15:8] -> A[18:16]

PIP Layer Y Start Position Register

Start Position

D[7:0]

1 0 0

PIP Layer Y Start Position

P2

D[15:8]

PIP Layer Y

These bits specify Y start position of the PIP Layer on the panel, in lines

1 0 0 n/a n/a n/a n/a n/a n/a

Start

Position

PIP Enable

P1 60860 0 0 0

A[7:0]-> A[15:8] -> A[18:16]

PIP Enable Register

D[7:0]

Blink/

Bit[2:0] = 000b, Blank

Fade

Bit[2:0] = 001b, Normal

1 0 0 n/a n/a n/a n/a

Blink/Fade Effect

Status

Bit[2:0] = 010b, Blink 1

(RO)

Bit[2:0] = 011b, Blink 2

D[15:8]

Bit[2:0] = 100b, Fade Out

P2

Bit[2:0] = 101b, Fade In

Bit[2:0] = 110b, Fade In/Out Continuous

1 0 0

Blink/Fade Period

n/a Bit[2:0] = 111b, Reserved

Bit[3] = 0b, the PIP layer is not blinking or fading

Bit[3] = 1b, the PIP layer is in the process of blinking or fading

Bit[15:9] = blink/fade period in frames – 1

Alpha

P1 60862 0 0 0

A[7:0]-> A[15:8] -> A[18:16]

Alpha Blending Register

Blending

D[7:0]

1 0 0 n/a

Alpha Blending Ratio

Bit[6:0] = 0000000b,0000001b… …0111111b,1000000b :

D[15:8]

64:0 (no PIP),63:1 … … 1:63,0:64(full PIP) ;

1000001b ~ 1111111b : Reserved

P2

Alpha

Bit[9:8] = 00b, 1

1 0 0 n/a n/a n/a n/a n/a n/a

Blending

Bit[9:8] = 01b, 2

Step

Bit[9:8] = 10b, 4

Bit[9:8] = 11b, 8

Transparency P1 60864 0 0 0

A[7:0]-> A[15:8] -> A[18:16]

Transparency Register

D[7:0]

Transp

1 0 0 n/a n/a n/a n/a n/a n/a n/a arency Bit[0] = 0b, transparency is disabled

P2

Enable Bit[0] = 1b, transparency is enabled

D[15:8]

1 0 0 n/a n/a n/a n/a n/a n/a n/a n/a

Transparency P1 60866 0 0 0

A[7:0]-> A[15:8] -> A[18:16]

Transparency Key Color Register 0

Key Color 0

D[7:0]

Key Color Blue

Bit[15:8] is Key Color Green bits [7:0]

P2

1 0 0

D[15:8]

1 0 0

Key Color Green

Bit[7:0] is Key Color Blue bits [7:0]

Transparency P1 60868 0 0 0

A[7:0]-> A[15:8] -> A[18:16]

Transparency Key Color Register 1

Key Color 1

D[7:0]

Key Color Red

P2

1 0 0

Bit[7:0] is Key Color Red bits [7:0]

D[15:8]

1 0 0 n/a n/a n/a n/a n/a n/a n/a n/a

GPIO

P1 608D0 0 0 0

A[7:0]-> A[15:8] -> A[18:16]

GPIO Configuration Register

Configuration

D[7:0]

Bit[15:0] = 0b (default), the corresponding GPIO pin is configured as an

1 0 0 GPIO7 GPIO6 GPIO5 GPIO4 GPIO3 GPIO2 GPIO1 GPIO0

Config

Config

Config

Config

Config

Config

Config

Config input pin

P2

D[15:8]

Bit[15:0] = 1b , the corresponding GPIO pin is configured as an output pin

1 0 0 GPIO15 GPIO14 GPIO13 GPIO12 GPIO11 GPIO10 GPIO9 GPIO8

Config

Config

Config

Config

Config

Config

Config

Config

GPIO Status P1 608D2 0 0 0

A[7:0]-> A[15:8] -> A[18:16]

GPIO Status and Control Register

and Control

D[7:0]

1 0 0 GPIO7 GPIO6 GPIO5 GPIO4 GPIO3 GPIO2 GPIO1 GPIO0 When GPIOx is configured as an output:

Status

Status

Status

Status

Status Status

Status

Status

P2

Bit[15:0] = 0b, GPIOx low

D[15:8]

1 0 0 GPIO15 GPIO14 GPIO13 GPIO12 GPIO11 GPIO10 GPIO9 GPIO8 Bit[15:0] = 1b, GPIOx high

Status

Status

Status

Status

Status

Status

Status

Status

GPIO Pull-

P1 608D4 0 0 0

A[7:0]-> A[15:8] -> A[18:16]

GPIO Pull-Down Control Register

Down Control

D[7:0]

GPIO7

GPIO6

GPIO5

GPIO4

GPIO3

GPIO 2

GPIO1

GPIO0

1 0 0 Pull- Pull- Pull- Pull- Pull- Pull- Pull- Pull-

down

down

down

down

down

down

down

down

Bit[15:0] = 0b, the pull-down resistor for the associated GPIO pin is

Control

P2

Control

Control

Control

Control

Control

Control

Control

inactive.

D[15:8]

GPIO15 GPIO14 GPIO13 GPIO12 GPIO11 GPIO10 GPIO9

GPIO8

Bit[15:0] = 1b, the pull-down resistor for the associated GPIO pin is active.

1 0 0 Pull- Pull- Pull- Pull- Pull- Pull- Pull- Pull-

down

down

down

down

down

down

down

down

Control

Control

Control

Control

Control

Control

Control

Control

Note: Access of PLL Setting 0, PLL Setting 1, PLL Setting 2 and Internal Clock Configuration is only possible

in Power Save Mode PSM0.

For more information and details please refer to S1D13L01 datasheet.

RL:

www.topwaydisplay.com

Document Name: LMT043DNFFWD-NCA-Manual-Rev0.4

Page: 13 of 16

TOPWAY

LCD Module User Manual

LMT043DNFFWD-NCA

10. Touch panel Design Precautions

1. It should prevent front case

touching the touch panel

Active Area (A.A.) to prevent

abnormal touch.

It should left gab (e.g.

0.2~0.3mm) in between.

2. Outer case design should take care about the area outside the A.A.

Those areas contain circuit wires which is having different thickness. Touching those areas could de-

form the ITO film. As a result case the ITO cold be damaged and shorten its lifetime.

It is suggested to protect those areas with gasket (between the front case and the touch panel).

The suggested figures are B≥0.50mm; C≥0.50mm 。

3. The front case side wall should keep space

(e.g. 0.2 ~ 0.3mm) from the touch panel.

4. In general design,

touch panel V.A. should be bigger than the LCD V.A.

and touch panel A.A. should be bigger than the LCD A.A.

RL:

www.topwaydisplay.com

Document Name: LMT043DNFFWD-NCA-Manual-Rev0.4

Page: 14 of 16

TOPWAY

LCD Module User Manual

LMT043DNFFWD-NCA

11. Precautions of using LCD Modules

Please refer to "LCD-Module-Design-Handling-Precaution.pdf".

12. Appendix A Inspection items and criteria for appearance defects

Items

Criteria

Open Segment or Common

N OT PERMITTED

Short

Not permitted

Wrong Viewing Angle

Not permitted

Decliners

Not permitted

Contrast Ration Uneven

According to the limit specimen

Crosstalk

According to the limit specimen

White spots

X>1 pixel

A-area

Not permitted

M AX 6 SPOTS

B-area

Max. 1 allowed

ALLOWED

1/2 pixel<X≤1 pixel

A-area

Not permitted

B-area

Max. 2 allowed

X≤1/2 pixel

A-area

Max. 1 allowed

B-area

Max. 4 allowed

Black Sport

X>1 pixel

A-area

Not permitted

B-area

Max. 2 allowed

X≤1/2 pixel

A-area

Max. 1 allowed

B-area

Max. 4 allowed

Line Defect

Apparent vertical horizontal line defects are not permitted

Notes:

1. On Pixel includes 3 dots (RedDot + GreenDot + BlueDot)

2. Definition of Panel “A-area” and “B-area”

RL:

www.topwaydisplay.com

Document Name: LMT043DNFFWD-NCA-Manual-Rev0.4

Page: 15 of 16